4 Entwickeln des Platinenlayouts

- Für die Laborleitung: Erstellen des Nutzens

Prozess 4: Entwickeln des Platinenlayouts

| Input Products | Work | Output Products |

|---|---|---|

| IP1. Schaltplan der Platinen | W1. Durchsicht der benötigten Datenblätter W2. Erstellen der Schaltung (*.sch) in eagle (Ändern eines vorandenen Boards) W3. Regelmäßige Durchsprache mit dem Betreuer W4. Ablegen der genutzten Datenblätter W5. Informieren des Betreuers | OP1. Schematic-files OP2: Datenblätter |

| Input Condition | Output Condition | |

| IC1. Schaltplan vom Betreuer abgenommen | OC1. Files abgelegt | |

| checkliste_fuer_das_layout | ||

101 - Layout zeichnen

Boardgröße und -typ

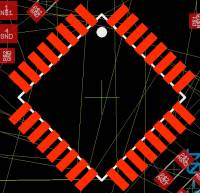

Beachten Sie, dass durch das Mexlesystem die Größe des Boards in verschiedenen Stufen vorgegeben ist (siehe figure 1). Eine Übersicht zum Mexle-Format ist unter der Beschreibung des MEXLE-Systems zu finden. Im Folgenden sind die verschiedenen MEXLE-Board-Größen und -Typen beschrieben:

| Funktion | Zweck | Einzoll-Board / Standard-Board | Viertelzoll-Board | Mehrzoll-Board | Hookup-Board |

|---|---|---|---|---|---|

| Anwendung | kleine Sensor/Aktor- oder Microcontroller-Boards | Diskrete Elemente, die auf die Eckjumper zurückgreifen. | größere Sensor/Aktor- oder Microcontroller-Boards | Sensor/Aktor-Boards | |

| Abmaße / Form | - Quadratischer Form mit abgerundeten Ecken (Radius $R=100 ~\rm mil$) - $1000 ~\rm mil \cdot 1000 ~\rm mil$. - Da zwischen zwei Standardboards auf dem Modulträger $100 ~\rm mil$ liegen, sind ausnahmsweise auch Maße zu $1100 ~\rm mil$ zulässig. | - Rechteckige Form ohne abgerundeten Ecken (geritzte Platine). - $1000 ~\rm mil \cdot 250 ~\rm mil$ | - Rechteckige Form mit abgerundeten Ecken (Radius $R=100 ~\rm mil$). - $1100 ~\rm mil \cdot (n-1) + 1000 ~\rm mil$ mit $n=\{1 ... 3 \}$ - $n$ ist dabei die Anzahl der Module, welche überdeckt werden. - Ein Mehrzoll-Board überstreckt sich über mehrere Module des Modulträgers. | - Rechteckige Form mit abgerundeten Ecken (Radius $R=100 ~\rm mil$). - $1000 ~\rm mil \cdot 1000 ~\rm mil$. - Da zwischen zwei Standardboards auf dem Modulträger $100 ~\rm mil$ liegen, sind ausnahmsweise auch Maße zu $1100 ~\rm mil$ zulässig. |

|

| Eckjumper $\rm SPx$ | - Verbindet das Board mechanisch mit dem Modulträger. - Eckjumper sind mit den Eckjumpern der benachbarten Boards elektrisch verbunden | Jumper ($\rm SP1... SP4$). Im Notfall sind die oberen beiden und der Jumper $\rm JP1$ zur mechanischen Fixierung ausreichend. | Jumper ($\rm SP1$ und $\rm SP2$). | Von den Eckjumpern sind nicht alle notwendig. Es wird empfohlen nur die äußersten vier Eckjumper zu nutzen. | Nicht notwendig, da für ein Hookupboard i.d.R. keine Notwendigkeit für ein aufstecken auf das Basisboard besteht. |

| Modul- versorgung $\rm JP1$ | - Der zweireihige Jumper $\rm JP1$ dient zur Stromversorgung und Datenkommunikation mit dem Modulträger. - Er ist optional. - Eine Datenkommunikation über I2C sowie die Stromversorgung sollten aber aus Kompatibilitätsgründen darüber geleitet werden. - Ist nur eine Stromversorgung notwendig, so kann ein einreihiger Jumper genutzt werden. | Der Jumper $\rm JP1$ sollte wie auf der mmc_1x1_328pb-Platine zu sehen positioniert werden | Der Jumper $\rm JP1$ liegt (wie die beiden Eckjumper) auf der Symmetrieachse | Auch hier sind wieder mehrere Positionen für $\rm JP1$ möglich. Es kann eine der möglichen (auf dem Raster des Modulträgers liegende) Positionen genutzt werden | Nicht notwendig, da für ein Hookupboard i.d.R. keine Notwendigkeit für ein aufstecken auf das Basisboard besteht. |

| Buchsen $\rm K1$ und $\rm K2$ | - Die Buchsen $\rm K1$ und $\rm K2$ dienen des Anschlusses von Hookup-Boards. - Er ist optional. - Falls Hookups ermöglicht werden sollten, so sind für die mechanische Stabilität beide Buchsen vorzusehen. - Ggf. kann die Buchse durch eine SMD-Buchse ersetzt werden | Sollen bei Mehrzoll-Boards eine Hookup-Möglichkeit zur Verfügung gestellt werden, so sind für die mechanische Stabilität zwei Buchsen ($\rm K1$ und $\rm K2$) vorzusehen, die $800 ~\rm mil$ auseinander liegen. Eine Position wie beim Standardboard wird empfohlen. | |||

| Pin-Belegung | Details zur Belegung von $\rm K1$, $\rm K2$, und $\rm JP1$ sind unter mmc_1x1_328pb beschrieben. Die dortige Belegung sollte aus Kompatibilitätsgründen eingehalten werden. | ||||

| eagle-Vorlage | Siehe 3. Entwickeln des Schaltplans | ||||

Erste Schritte im Leiterplatteneditor

Es kann sein, dass Sei beim Öffnen des Leiterplatteneditors folgende Fehlermeldung erhalten:

Fehler traten beim Laden der Footprints auf:

Footprint library 'C:\Program Files\KiCad\8.0\share\kicad\footprints\/Connector_HDMI.pretty' not found.

Dies ist leicht durch folgende Schritte lösbar.

- Gehen Sie zu

Einstellungen»Footprintbibliotheken verwalten … - Suchen Sie dort die angegebenen Ordner (in oben genannten Beispiel: “

Connector_HDMI.pretty” ) und deaktivieren Sie diesen Eintrag über den Haken in der Spalte “aktiv”

Bauteilpositionierung

Fig. 2: Beispiel für schlechte Anordnung für ein seitlich-bedienbare Taster

Fig. 2: Beispiel für schlechte Anordnung für ein seitlich-bedienbare Taster

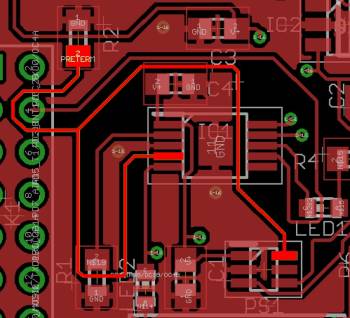

Fig. 3: Beispiel für schlechtes Airwiring

Fig. 3: Beispiel für schlechtes Airwiring

- Positionieren Sie immer als erstes die Bauteile.

- Denken Sie dabei in Baugruppen. Wenn für ein Spannungsregler der Kondensator C12 notwendig ist, dann sollten diese beiden Komponenten zusammenbleiben. Diese bilden eine “Baugruppe”

- Interface first: Erst geben meist die HMI-Komponenten (HMI: Human-Machine-Interface) und weitere Schnittstellen die Positionierung vor. Z.B. weil die die Tasten nebeneinander oder der USB-Anschluss außen zu positionieren ist. Außerdem sollten zusammenhängende Komponenten zusammenhängend platziert werden. Ein Bereich nur für Leistungselemente (z.B. Motorsteuerung), ein Bereich für externe Analog-Digital-Wandler, ein Bereich für schnell-schaltende ICs (z.B. Mikrocontroller).

- Dann sollten die großen Bauteile (ICs), dann die kleinen. Bei gleichen/ähnlichen ICs sollten die Kerben (bzw. Markierungen) in die gleiche Richtung zeigen, um ein Verdrehen zu vermeiden.

- Bei Mikrocontrollern und anderen vielbeinigen Chips bietet sich ein mehrmaliges Drehen um 45° an. Damit ist kann eine optimale Ausrichtung gesucht werden, welche kurze Leitungslängen erzeugt (siehe Bild).

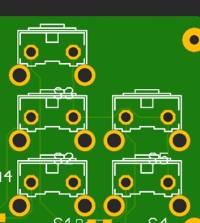

- Prüfen Sie bei Kondensatoren, ob diese möglichst in der Nähe von Bauteilen positioniert werden sollen. Als Faustformel gilt für Bypass-Kondensatoren, dass zwischen Kondensator -Anschluss und VCC-Pin sowie Kondensator-Anschluss und GND-Pin entlang der Leitung nur wenige Millimeter liegen.

- Richten Sie das “Vogelfutter” - also passive Bausteine, wie Widerstände und Kondensatoren - möglichst parallel aus. Bevor Sie tatsächlich Verbindungen ziehen, versuchen Sie das Vogelfutter so zu positionieren, dass es möglichst wenig Überschneidungen der Airwires gibt.

- Versuchen Sie möglichst alle Bauteile auf einer Seite, nämlich der Oberseite, zu positionieren.

- Falls der Platz nicht mehr ausreicht, empfiehlt sich folgende Reihenfolge bei der Auswahl der Komponenten für die Rückseite

- Lötjumper (SJxx)

- Vogelfutter (nicht Bypass- oder Filter-Komponenten)

- Komponenten die aufgrund der Größe oder Anwendung auch auf die Rückseite passen (z.B. nicht große Spulen, Schalter, LEDs)

- Positionieren Sie die Bauteile so auf dem Raster, dass Ein- und Ausgänge auf dem Raster liegen. Hierfür kann ein grobes Raster gewählt werden (z.B. 50mil).

- Wir nutzen eine aufgedruckte Beschriftung.

- Beschriften Sie also die Bauteile mit dem korrekten Namen (R1, C1, etc.) und setzen Sie die Beschriftung in die Nähe des Bauteils.

- Die Beschriftung darf nicht über blankem Kupfer (Pads) laufen und sollte nach Möglichkeit auch bei bestückter Platine sichtbar sein.

- Vergessen Sie nicht eine aussagekräftige Beschreibung für das Board zu nehmen (Autor, Projekt, Datum, etc).

- Die Beschriftung ist in KiCAD z.B. über die 3D Ansicht (

Ansicht » 3D-Betrachter) überprüfbar. - Die Beschriftung sollte mindestens $0.8~\rm mm$ Breite und Höhe haben. Falls Sie die Schriftgröße global verändern wollen, so nutzen Sie am besten folgende Schritte:

Bearbeiten»Text- und Grafikeigenschaften bearbeiten»Anwendungsbereich: Referenzbezeichnerund Anpassen der Textbreite und -höhe

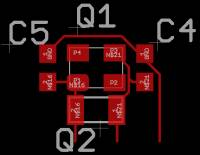

- Positionieren Sie Quarze und Oszillatoren unmittelbar in der Nähe der zu taktenden Komponente. Die Kondensatoren des Quarze sollten wiederum unmittelbar in der nähe der Quarz liegen (siehe Bild). Für den Abstand über die Leitung gilt Ähnliches wie bei den Bypass-Kondensatoren. Zusätzlich sollten keine Signale unter dem Quarz verlaufen.

- Eingangsfilter für Signale (z.B. bei Analogeingängen) empfiehlt sich auch möglichst nahe am IC zu positionieren. Ansonsten kann die Filterwirkung durch Übersprechen und die Leitungsimpedanz gestört werden.

Routing

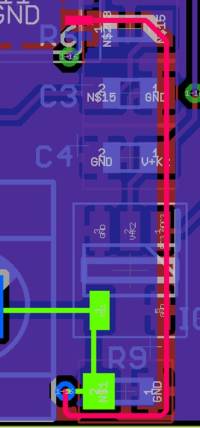

Fig. 6: Beispiel: schlecht verlegte Masseleitung (starke Wärmeableitung über blau markierte Verbindung)

Fig. 6: Beispiel: schlecht verlegte Masseleitung (starke Wärmeableitung über blau markierte Verbindung)

Fig. 7: gut verlegte Masseleitung

Fig. 7: gut verlegte Masseleitung

- Um das Routing zu vereinfachen, sollten auf Top bevorzugt die horizontale Verbindungen, auf Bottom die vertikale Verbindungen gelegt werden - oder umgekehrt. Diese Methode wird als Manhattan-Routing bezeichnet. Wenigstens sollten Sie die Verbindungen auf Top und Bottom senkrecht aufeinander stehen.

- der richtige Winkel: Allgemein sind spitze Winkel bei der Verbindungsführung zu vermeiden, da es dort zu Fertigungsproblemen kommen kann. Wenn von einem Pin mehrere Abgänge ausgehen, so ist folgendes zu unterscheiden: bei Masseanschlüsse sollen die Abgänge im 90° Winkel liegen (siehe Bild rechts). Alle anderen Winkel auf einer Ebene sollen in einem möglichst großen Winkel erfolgen, also 135°. Bei Vias mit jeweils einem Abgang dürfen beliebige Winkel genutzt werden.

- Es ist folgende Reihenfolge für das Routing empfohlen:

- Verbinden Sie zunächst alle Bypass-Kondensatoren an die jeweiligen Pins. Achten Sie dabei darauf, dass die Länge der Leitung minimal sein soll.

- Am zweitwichtigsten sind die Anbindung an Oszillator und Quarz, sowie deren Kondensatoren. Vermeiden Sie dabei (viele) Vias und versuchen Sie kurze Verbindungen zu setzen. Die Verbindungen sollten möglichst auf der Seite der entsprechenden Pins verlaufen.

- Ziehen Sie als nächstes die Leitungen für die analoge und digitale Datenübertragung. Auch hier auf wenig (bis keine) Vias, kurze Verbindungen und gleiche Seite wie die ausgehenden Pins achten.

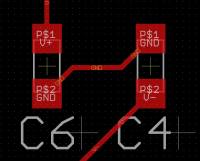

- Danach ist die Spannungsversorgung zu verbinden. Hier sollte - soweit möglich - eine breitere Leitung (z.B. $10~\rm mil$ bzw. $0.25~\rm mm$ oder größer) genutzt werden.

- Schließen Sie dann alle GND per Verbindungen an den Masseanschluss an. Achten Sie darauf, Versorgungsmassen (GND) von der Masse für Analogeingänge (AGND) zu trennen.

- Für die Leiterbahnen sollte $0.2~\rm mm$ ($6~\rm mil$ oder $8~\rm mil$) als Standardbreite genutzt werden. Wenn Platz vorhanden ist, schadet eine breitere Leitung bis $0.25~\rm mm$ ($10~\rm mil$) nicht. Beachten Sie ab Strömen von ca. $1~\rm A$ die Strombelastbarkeit von Leiterbahnen. Bei größeren Strömen erwärmen sich die Leitbahnen unter Umständen stark. Mit steigender Temperatur können sich die Werte von Kondensatoren, Widerständen und weiteren Komponenten ändern. Eine Berechnung der der Temperaturänderungen finden Sie in kiCAD im Projektfenster unter

Berechnungswerkzeuge»Leiterbahnbreite. Temperaturen unter $70~\rm °C$ sind akzeptabel. Daraus ergeben sich bei einer Raumtemperatur von bis zu $30~\rm °C$ einen maximalen Temperaturanstieg von $40~\rm °C$. - Für Vias können bis zu einem Drill von $=0.2~\rm mm$ ($7.87402~\rm mil$) genutzt werden. Für geringe Stückzahlen sind diese nicht teurer.

Wichtig auch hier: wenn viel Strom ($\gtrapprox 1...2~\rm A$) über ein Vias transportiert werden soll, sind größere Vias und/oder mehrere Vias besser. Für Details hat kiCAD im Projektfenster einen “Werkzeug-Koffer” an:Berechnungswerkzeuge»Via-Größe - Legen Sie abschließend auf jede genutzte Ebene ein gefüllte Zone (

<Strg>+<Umschalt>+Z, auch Polygon genannt) und benennen Sie es “GND”. Dann können Sie mit Ratsnest die Freiflächen mit Masse ausfüllen. Damit reduziert sich Störausstrahlung, induktive Verluste und Widerstand zu Masse. Gibt es neben GND auch AGND, so bietet sich auch ein separate AGND-Fläche an. - Suchen sie in den Dokumenten der Komponenten (“application notes” oder “data sheet”) nach “Layout”, “Layout Guidelines” oder “Layout Examples”. Falls Sie dort keine Beispiele finden, lohnt sich ein nachdenklicher Blick auf Platinenhersteller. Bei Open Source Herstellern wie Adafruit oder Sparkfun können dazu meist Erklärungen zur Schaltung gefunden werden (z.B. für Motortreiber). Diese Vorarbeit erleichtert nicht nur das Layout, sondern reduziert auch die Wahrscheinlichkeit von Problemen!

- Falls Sie differentielle, digitale Signale (z.B. D+ und D- bei USB) routen, beachten Sie, dass die Verbindungen so gut wie möglich gleich lang sein sollten. Gleiches gilt für differentielle, analoge Signale mit hochfrequentem Nutzanteil. Weitere Tipps und Tricks finden Sie im Video differential Pairs und in der Anleitung How to route differential pairs.

- Kann ich auch Vias in Pads setzen? Es kommt darauf an: Verwenden Sie eine Pick-and-Place System mit Lötpaste, dann sollten keine (großen) Vias in Pads gesetzt werden. Ansonsten wird im Reflow-Ofen das Lot durch das Via fließen, womit zu wenig Lot zum Verbinden des Bauteils vorhanden ist. Wenn Sie als Via Drill $≤0.3~\rm mm$ ($= 11.811 ~\rm mil$) verwenden, dann kann dies weniger problematisch, da der „suck down“ aufgrund der Oberflächenspannung des Lötzinns merklich geringer ausfällt. Auch beim händischem Löten tritt das Problem weniger auf.

Generell sollten Vias in Pads in der Elektronik vermieden werden. - Ich habe zu viele Verbindungen und kann in der Schaltung nichts mehr finden. Öffnen Sie den Schaltplaneditor neben dem Leiterplatteneditor. Dann sind im Schaltplaneditor hervorgehobene Komponenten und Verbindungen auch im Leiterplatteneditor markiert. Weiterhin können Verbindungen mit auch unterschiedliche Farben markiert werden: rechts im Leiterplatteneditor

Netze»Netz-Anzeigeoptionen»Netzfarben: Alle. Nun können im oberen Bereich die Farben vergeben werden.

weitere Routing Iteration

Es bietet sich - wie bei der Software-Entwicklung - an nach der ersten “fertigen Version” nochmals die Entwicklung zu betrachten und Korrekturen vorzunehmen.

Dies betrifft bei der Platine insbesondere die folgenden Punkte.

unnötig lange Leitungen

Vermeiden Sie lange Leitungen, insbesondere wenn diese eine große Fläche umschließen. Damit entstehen unter Umständen Empfänger für eine induktive Kopplung.

Häufig hilft auch bei langen Leitungen zu überlegen, ob ein Verschieben und Drehen von Komponenten die Wege verkürzt.

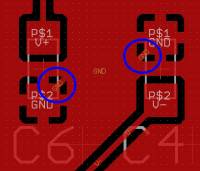

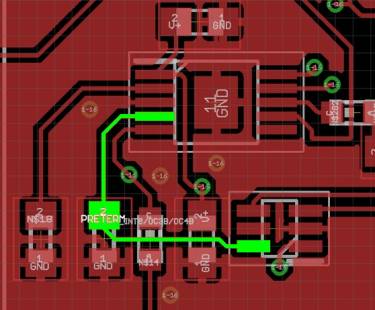

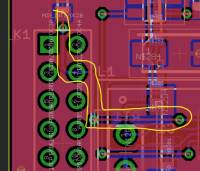

Fig. 8: Beispiel: unnötig lange Verbindungen (rechts: Verbesserung)

Fig. 8: Beispiel: unnötig lange Verbindungen (rechts: Verbesserung)

Fig. 9: Beispiel: unnötig lange Verbindungen (rechts: Verbesserung)

Fig. 9: Beispiel: unnötig lange Verbindungen (rechts: Verbesserung)

unnötige Vias

Bei Vias sollte geprüft werden, ob diese tatsächlich notwendig ist. Auch bei der Anwendung von Manhattan-Routing hilft eine abschließender Check ob der Layer-Wechsel notwendig ist.

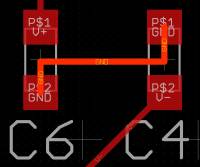

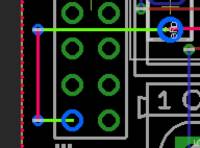

Fig. 10: zwei unnötige Vias: THD-Komponenten können von beiden Seiten angeschlossen werden. (rechts: Verbesserung)

Fig. 10: zwei unnötige Vias: THD-Komponenten können von beiden Seiten angeschlossen werden. (rechts: Verbesserung)

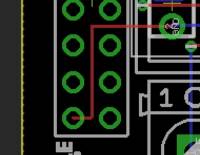

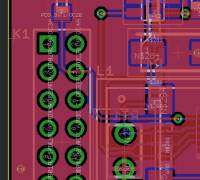

Fig. 11: zwei unnötige Vias (rechts: Verbesserung)

Fig. 11: zwei unnötige Vias (rechts: Verbesserung)

leichte Bestückung

Um die Bestückung zu vereinfachen, sollten die passiven Komponenten gleichartig angeordnet werden. Insbesondere gilbt das für Dioden - hier sollten immer die parallele Anordnung der antiparallelen bevorzugt werden.

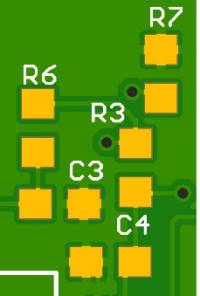

Fig. 12: Beispiel: unsortierte Passivkomponenten (rechts: Verbesserung)

Fig. 12: Beispiel: unsortierte Passivkomponenten (rechts: Verbesserung)

Via in Pads

Vias in Pads sollten vermieden werden. Hierdurch wird das Lötzinn auf die andere Seite gezogen. Damit kann die Verbindung zum Pad schlechter werden.

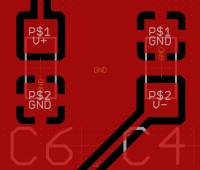

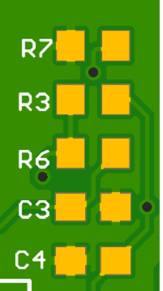

Fig. 13: Beispiel: unsortierte Passivkomponenten (rechts: Verbesserung)

Fig. 13: Beispiel: unsortierte Passivkomponenten (rechts: Verbesserung)

Bauteil-Erstellung

- Versuchen Sie keine länglichen Pads ( = Lötaugen) zu verwenden (z.B. bei manchen Through-Hole Komponenten). Falls eine Komponente aus der Lib solche Pads enthält, können Sie wie folgt vorgehen:

(1) Export der Komponente aus der Schematic-Darstellung (Datei » Exportieren » Libraries und Auswahl der gewünschten Komponenten)

(2) Öffnen der Komponente

(3) Auswahl der Footprint Darstellung

(4) Change-Funktion aktivieren (Schraubenschlüssel) » Shape » round

(5) alle gewünschten Pads anklicken

(6) ersten Pad auswählen und dieses als Quadrat ausführen. (Rechtsklick » Eigenschaften » Shape » Square)

(7) Abspeichern und in brd als neue library einbinden - die schnelle Alternative zum eigen erstellten Footprint ist die Suche in größeren Libraries. Dazu bietet sich an:

- SameSkyDevices (auch für 3D Modelle)

- die Suche über Google z.B.

<Bauteilname> lib site:github.com. Statt nach “lib” kann auch nach “sch” gesucht werden. Die Library lässt sich in eagle schnell aus der schematic exportieren. - die Komponente muss auch nicht exakt übereinstimmen. So kann auch die Suche nach einer Komponente mit gleichem Footprint oder direkt nach der Bezeichnung des Footprints weiterhelfen

Zum Abschluss

- Design Rule Check durchführen:

Inspektion»Designregeln überprüfen (DRC)

Bitte achten Sie darauf, dass auch der Bestückungsdruck geprüft wird.

Dazu Folgendes prüfen:Datei»Platinenkonfiguration»Verstoß-Schweregrade»Lesbarkeit»Bestückungsdrucküberlappung --> als Warnung

Folgendes sind häufige Findings:

Fehler: Elemente, die zwei Netze kurzschließen (Netze X und Y):

Ein Pad hat Kontakt mit einer Leiterbahn, welche auf einem anderen Potential liegt (z.B. nach Verschieben von Komponenten). Komponente und/oder Leiterbahn ist zu verschieben.

Fehler: Leiterbahnkreuzung:

Eine Leiterbahn hat Kontakt mit einer Leiterbahn, welche auf einem anderen Potential liegt (z.B. nach Verschieben von Komponenten). Leiterbahn(en) ist/sind zu verschieben.

Fehler: Abstandsflächenüberschneidung:

Zwei Komponenten kommen such zu nahe, sodass es eine Überlappung ihrer 'Courtyards' gibt. Komponente(n) ist/sind zu verschieben.

Fehler: Vorderseitige Lötstoppöffnung über Elementen mit verschiedenen NetzenbzwFehler: Rückseitige Lötstoppöffnung über Elementen mit verschiedenen Netzen:

Zwei Komponenten kommen such zu nahe, sodass es eine Überlappung ihrer Lötstoppöffnungen (z.B. Pads) gibt. Komponente(n) ist/sind zu verschieben.

Fehler: Platinenkanten-Freiraum-Verstoß:

Abstand eines Pads zum Rand ist zu kurz. Komponente verschieben.

Fehler: Freiraum-Verstoß (Netzklasse “Default” Freiraum X; tatsächlich Y):

Falls dieser Fehler zwischen zwei Komponenten liegt, ist mindestens eine der beiden zu verschieben.

Falls es innerhalb einer Komponente vorhanden ist, so liegt dies häufig an den “Benutzerdefinierten Regeln”: Diese können Sie überDatei»Platinenkonfiguration»Designregeln»Benutzerdefinierte Regelnfinden. Hier sollten nichts in der Textbox stehen. Falls die Textbox nicht leer ist, ist diese zu leeren.

Fehler: Freiraum-Verstoß (Regel “class 0:0” Freiraum X; tatsächlich Y):

Falls dieser Fehler zwischen zwei Komponenten liegt, ist mindestens eine der beiden zu verschieben.

Falls es innerhalb einer Komponente vorhanden ist, so liegt dies häufig an den “Netzklassen”: Diese können Sie überDatei»Platinenkonfiguration»Designregeln»Netzklassenfinden. Hier sollten die folgenden Werte auftauchen:

Fehler: Platinenkanten-Freiraum-Verstoß (Einschränkungen aus Platinenkonfiguration zum Rand Freiraum X; tatsächlich Y):

Dies liegt häufig an den “Einschränkungen”: Diese können Sie überDatei»Platinenkonfiguration»Designregeln»Einschränkungenfinden. Hier sollten die folgenden Werte auftauchen:

Warnung: Leiterbahn hat unverbundenes Ende:- Alle Airwires sind zu verbinden.

- Bei Ground muss beachtet werden, dass alle einzelnen Groundflächen verbunden sind. Falls es dort “unauffindbare” Probleme gibt, bietet es sich an alle GND-Anschlüsse mit Routes zu verbinden

- Speziell für die Versorgung mit +3V3 ist prinzipiell nur ein Pin der beiden Stecker K1 und K2 notwendig. Der nicht benötigte Anschluss sollte bei Nicht-Verwendung über eine „Keine-Verbindung-Kennzeichnung“ (Markierung mit X) abgeschlossen werden.

Warnung: Via ist nicht oder nur auf einer Lage verbunden:

Ein Via ist nicht vollständig verbunden. Via verbinden.

Warnung: Bestückungsdruck von Platine abgeschnitten:- Der Bestückungsdruck sollte gänzlich auf der Platine liegen - der Text ist also vollständig auf die Platine zu schieben.

- Bei randständigen Komponenten sind Ausnahmen möglich, d.h. es kann diese Warnung unkorrigiert stehen gelassen werden.

Bei den MEXLE Vorlagen liegen die Bestückungsdrucke von JP1 bzw. K1 und K2 teilweise über dem Platinenrand. Diese können akzeptiert werden. - Sofern die Warnung beim Text von K1 und K2 erscheint, so kann dieser wiefolgt verschoben werden:

Warnung: Bestückungsdruck schneidet Lötstoppmaske:

Ein Bestückungsdruck liegt auf einer offenen Kupferfläche (z.B. Pad). Auf Kupfer hält der Bestückungsdruck nicht. Der Text ist zu schieben.

Falls der Text in einem gesperrten Element liegt, hilft es manchmal beim Auswahlfiltergesperrte Elementezu aktivieren

Warnung: Bestückungsdrucküberlappung:

Überlappung von Text / Bestückungsdruck ist zu vermeiden.

Warnung: Footprint “X” nicht in Bibliothek “Library” gefunden:

Der angegebene Footprint ist nicht im Projekt bekannt:

Dies lässt sich leicht lösen:- Rechtsklick auf betroffene Komponente und

Im Footprinteditor öffnen - im Footprinteditor:

Datei»Neue Bibliothek…»Projekt, im Folgenden den Pfad der Projektdaten auswählen (den Ordner, in welchem diese Dateien abliegen)» NameLibrary.pretty»Ordner auswählendrücken - im Footprinteditor:

Datei»Speichern unter…»Libraryauswählen und Footprinteditor schließen Einstellungen»Footprintbibliotheken verwalten…»Projektspezifische Bibliotheken» falls hier nicht die Bibliothek “Library” zu finden ist, so ist diese mit über dasOrdnersymboleinzufügen

Warnung: Isolierte Kupferfüllung:

Diese Warnung erscheint, wenn es durch eine Kupferzone kleine Kupferinseln gibt, welche nicht mit der Kupferzone verbunden verbunden ist. Häufig ist dies beim Groundlayer der Fall. Als Lösung sollte die Kupferzonen-Eigenschaften geändert werden: die OptionInseln entfernensollte aufImmeroderUnterhalb der Flächengrenzegesetzt werden. Alternativ hilft es über ein Via zum rückseitigen Groundlayer die Fläche zu füllen.

Zu beachten ist auch:

- Versorgung mit +3V3

- Diese kann sowohl über den Stecker K1 als auch über K2 oder über beide gleichzeitig geschehen.

- Wird die Versorgung nur von einem Stecker genutzt (z.B. K1), so sollte in der Schaltung beim anderen Stecker (im Beispiel K2) die Versorgung auf eine

keine-Verbindung-Kennzeichnungerhalten. Dann ergibt sich kein Fehler. - Wird die Versorgung nur von von beiden Steckern genutzt, muss keine Verbindung dazwischen vorgesehen werden.

In diesem Fall ergibt sich der VerstoßFehler: Fehlende Verbindung zwischen Elementen, welcher mit rechtsklick ausgeschlossen werden kann

Weiterhin ist zu prüfen:

- Polygonfüllung der Freiflächen mit Ground

- Füllen Sie die Polygone, seigen Sie diese an und und prüfen Sie nach ungefüllten Flächen:

- Füllen:

Bearbeiten»Alle Zonen füllen(oderB) - Anzeigen:

Ansicht»Zeichnungsmodus»Zonen-Füllungen zeichnen

- Keine Polygonfüllung sichtbar?

- Erstellen:

Hinzufügen»Gefüllte Zone hinzufügen(oder<Strg>+<Umschalt>+Zoder folgendes Icon)

- Nach dem ersten Klick außerhalb der Platinenrandflächen:

Einstellen der Kupferzonen-Eigenschaften

- Zeichnen für horizontale und vertikale Linien, welche zum Schluss am exakt gleichen Punkt enden, an dem begonnen wurde.

- 3D-Ansicht prüfen: Bestückungsdruck und Kupferflächen überprüfen